- 您现在的位置:买卖IC网 > Sheet目录3833 > PIC16LF84A-04I/SS (Microchip Technology)IC MCU FLASH 1KX14 EE 20SSOP

Micrel, Inc.

KSZ8851SNL/SNLI

August 2009

48

M9999-083109-2.0

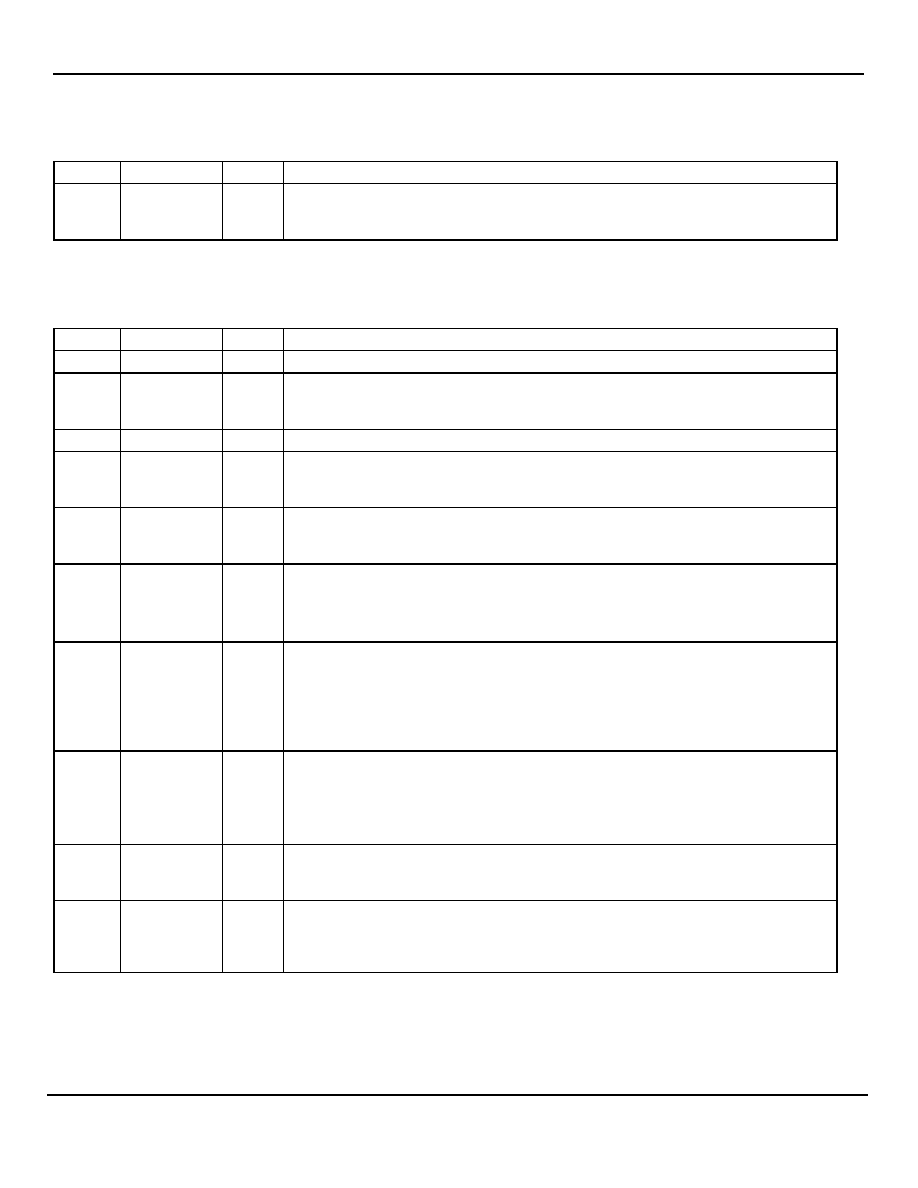

Wakeup Frame 3 Byte Mask 3 Register (0x6A – 0x6B): WF3BM3

This register contains the last 16 bytes mask values of the Wake up frame 3 pattern. Setting bit 0 selects the 49th byte

of the Wake up frame 3. Setting bit 15 selects the 64th byte of the Wake up frame 3.

Bit

Default Value

R/W

Description

15-0

0

RW

WF3BM3

Wake up Frame 3 Byte Mask 3. The last 16 bytes mask covering bytes 49 to 64 of a

Wake up frame 3 pattern.

0x6C – 0x6F: Reserved

Transmit Control Register (0x70 – 0x71): TXCR

This register holds control information programmed by the CPU to control the QMU transmit module function.

Bit

Default Value

R/W

Description

15-9

-

RO

Reserved

8

0x0

RW

TCGICMP Transmit Checksum Generation for ICMP

When this bit is set, The KSZ8851SNL is enabled to transmit ICMP frame (only for non-

fragment frame) checksum generation.

7

0x0

RO

Reserved

6

0x0

RW

TCGTCP Transmit Checksum Generation for TCP

When this bit is set, The KSZ8851SNL is enabled to transmit TCP frame checksum

generation.

5

0x0

RW

TCGIP Transmit Checksum Generation for IP

When this bit is set, The KSZ8851SNL is enabled to transmit IP header checksum

generation.

4

0x0

RW

FTXQ Flush Transmit Queue

When this bit is set, The transmit queue memory is cleared and TX frame pointer is reset.

Note: Disable the TXE transmit enable bit[0] first before set this bit, then clear this bit to

normal operation.

3

0x0

RW

TXFCE Transmit Flow Control Enable

When this bit is set and the KSZ8851SNL is in full-duplex mode, flow control is enabled.

The KSZ8851SNL transmits a PAUSE frame when the Receive Buffer capacity reaches a

threshold level that will cause the buffer to overflow.

When this bit is set and the KSZ8851SNL is in half-duplex mode, back-pressure flow

control is enabled. When this bit is cleared, no transmit flow control is enabled.

2

0x0

RW

TXPE Transmit Padding Enable

When this bit is set, the KSZ8851SNL automatically adds a padding field to a packet

shorter than 64 bytes.

Note: Setting this bit requires enabling the add CRC feature (bit1=1) to avoid CRC errors

for the transmit packet.

1

0x0

RW

TXCE Transmit CRC Enable

When this bit is set, the KSZ8851SNL automatically adds a 32-bit CRC checksum field to

the end of a transmit frame.

0

0x0

RW

TXE Transmit Enable

When this bit is set, the transmit module is enabled and placed in a running state. When

reset, the transmit process is placed in the stopped state after the transmission of the

current frame is completed.

Transmit Status Register (0x72 – 0x73): TXSR

This register keeps the status of the last transmitted frame.

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

5176916-1

HIGH CURRENT DRAWER 24P

PIC18F2520-I/SP

IC MCU FLASH 16KX16 28-DIP

PIC18F86J65-I/PT

IC PIC MCU FLASH 48KX16 80TQFP

PIC32MX320F064H-40I/MR

IC PIC MCU FLASH 64KB 64-QFN

PIC18F4423-I/P

IC PIC MCU FLASH 8KX16 40DIP

PIC18LF8390-I/PT

IC PIC MCU FLASH 4KX16 80TQFP

PIC18F2455-I/SO

IC PIC MCU FLASH 12KX16 28SOIC

TS87C51RD2-VCL

IC MCU 8051 OTP 64K 5V 68PLCC

相关代理商/技术参数

PIC16LF84A-04I/SS

制造商:Microchip Technology Inc 功能描述:8BIT FLASH MCU SMD 16LF84 SSOP28

PIC16LF84AT-04/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84AT-04/SS

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84AT-04I/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84AT-04I/SS

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84T-04/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF84T-04I/SO

功能描述:8位微控制器 -MCU 1.75KB 68 RAM 13 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC16LF870-I/SO

功能描述:8位微控制器 -MCU 3.5KB 128 RAM 22 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT